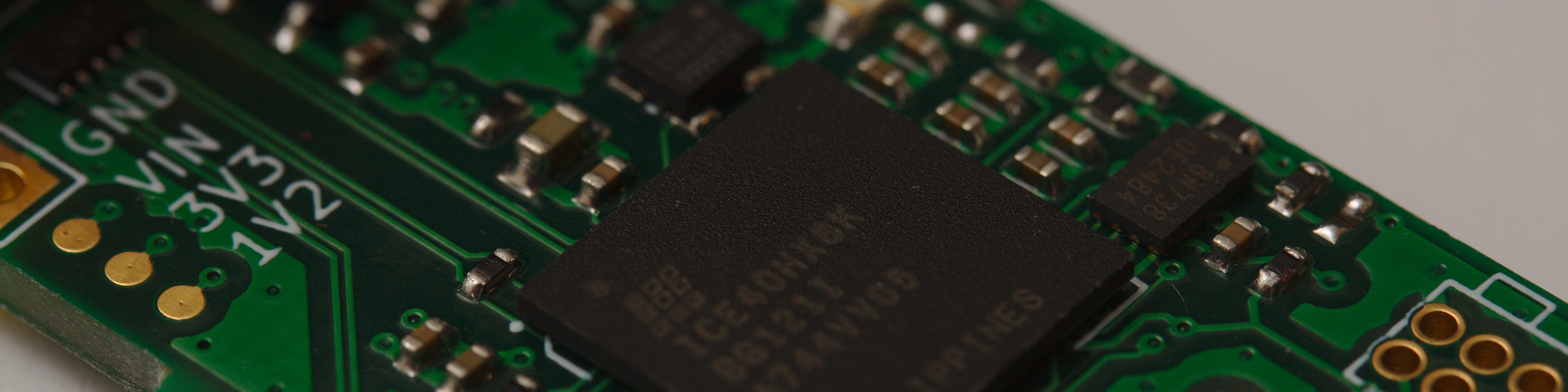

DAQnet is an experimental FPGA project to investigate some design concepts, especially implementing RMII for 100Mbps Ethernet and an IP/UDP stack on the iCE40 FPGAs. The goal was to have a central switch board and multiple sensor boards; the switch would connect to an IP network while the sensors would connect to the switch using CAT5 cabling but with a high-speed differential UART-style signalling protocol.

I successfully got a working Ethernet interface in the FPGA, which could handle ARP, ICMP, and UDP messages at full line rate.

My FPGA ethernet project now responds to ping! The MAC and IP stack are all written in nmigen, the IP stack runs at 100MHz on an iCE40HX. So it takes it 1µs to turn around a ping packet… pic.twitter.com/6VMZHPUdkN

— Adam Greig (@adamgreig) January 20, 2019

Currently the sensor board part of the project is unimplemented.